半加算と全加算

コンピュータは、内部的な仕組みとして、いくつかの論理演算で加算を実現している。 加算には、半加算と全加算がある。下図は、4ビット0101と0011を加算した結果を示したものである。

| 桁 | A | B | Cin | 和 (S) | Cout | 使用 |

|---|---|---|---|---|---|---|

| 3 | 0 | 0 | 1 | 1 | 0 | 全加算 |

| 2 | 1 | 0 | 1 | 0 | 1 | 全加算 |

| 1 | 0 | 1 | 1 | 0 | 1 | 全加算 |

| 0 | 1 | 1 | – | 0 | 1 | 半加算 |

下位桁(0)は、1と1という2つの数値を足すだけである。 これを半加算と呼ぶ。 2桁目(1)は、0と1と下位桁からの桁上がりの1という3つの数値を足す。 これを全加算と呼ぶ。 3桁目(2)と4桁目(3)も、3つの数値を足すので、全加算である。

半加算を2つ使うことで、全加算が実現されている。 これを逆に言うと、 全加算の半分で半加算が実現されている。 だから、 半加算と呼ぶのである。

半加算器の仕組み

論理回路を使って、 半加算を実現したものを半加算器 (half adder)と呼び、 全加算を実現したものを全加算器 (full adder) と呼ぶ。 それぞれの仕組みを説明しよう。

まず、半加算器である。 半加算器は、1ビットの数値を2つ足す。 足し合せる数値の組合わせは、 0+0=0、 0+1=1、 1+0=1、 1+1=10の4通りである。 1+1=10だけ桁上がりするので、他の演算結果も2桁に揃えると、 0+0=00、0+1=01、1+0=01、1+1=10になる。

下図は、ピットにX+Y=SCという名前を付けて、真理値表にしたものである。

CはCarry (桁上がり)、SはSUM (和) を意味する。

| X | Y | S(和) | C(繰上がり) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

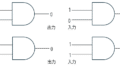

この真理値表を見ると、 XとYが両方とも1のときに、Cが1になることがわかる。 したがって、 C=XAND Yである。 XとYのどちらか一方だけが1のときに、Sが1になることがわかる。 したがって、 S=X XOR Y である。論理演算で、半加算が実現できた。 下図は、 MIL記号で半加算の仕組みみを示したものである。

MIL記号で示した半加算器の仕組み

全加算器の仕組み

全加算器は、その桁にある2つの数値X、Yと、下位桁からの桁上がりの数値C’の3つを加算し、 上位桁への桁上がりCと、 和Sを得る。 半加算器で、 2つの数値を足せるので、半加算器が2つあれば、3つの数値を足せる。 全加算器の桁上がりCは、 2つの半加算器のいずれかが桁上がりを起こしたときに1になる。 したがって、 OR 回路で求められる。 下図は、 MIL記 号で全加算器の仕組みを示したものである。

全加算器は、半加算器2つとOR回路で作れる。

半加算器を1つ、 全加算器を3つ用意して、下位桁の加算器のC出力を上位行の全加算器のC’ 入力につなげば、 4ビットの2進数の加算ができる。 この仕組みに、2の補数表現で表されたマイナスの数値を入力すれば、減算も行える。

マイナスの数値を加算することは、減算と同じだからである。

(参考)情報処理教科書 出るとこだけ!基本情報技術者[科目A][科目B]2025年版

コメント